|

Pile Of Garbage posted:apparently some heavy lifting has already been done in this area: Does anyone have the original thread link for Groverhaus? (haus? house?).

|

|

|

|

|

| # ? Apr 28, 2024 05:23 |

|

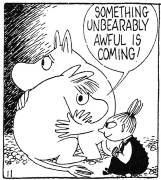

its beautiful

|

|

|

|

alexandriao posted:Does anyone have the original thread link for Groverhaus? (haus? house?). supposedly it's this one. i don't have archives so I'm not totally sure http://forums.somethingawful.com/showthread.php?threadid=2253640

|

|

|

|

Lutha Mahtin posted:supposedly it's this one. i don't have archives so I'm not totally sure

|

|

|

|

Phrases like "load bearing drywall" will only make you wish deeply for pictures.

|

|

|

|

I forgot how awful the 6502's lack of registers and weird addressing modes are. But I got a hello world for the NES working over the thanksgiving vacation.

|

|

|

|

ullerrm posted:I forgot how awful the 6502's lack of registers and weird addressing modes are. But I got a hello world for the NES working over the thanksgiving vacation. DOES IT EVER HIT THE CORNERS AADDHSJAHABDNJXJDEHDF

|

|

|

|

ullerrm posted:I forgot how awful the 6502's lack of registers and weird addressing modes are. But I got a hello world for the NES working over the thanksgiving vacation. But the zero page is like having 256 registers! Each half the size of a memory address, requiring at least 3 instructions to add any two of them and store the result back... fine, the 6502 is garbage.

|

|

|

|

6809 is supposed to be way better but I never really looked into its asm

|

|

|

|

The 6809 and 6800 both at least had a 16-bit stack pointer and index register. The 6502 was way down in the weeds on cost vs everything else so of course a ton of home computers used it. All of the popular 8-bit big-endian CPUs call the stack ops push and "pull" so there's going to be uncomfortable cringing involved no matter what.

|

|

|

|

BobHoward posted:6809 is supposed to be way better but I never really looked into its asm the 6809 owns. it actually has a useful number of registers and its indexed addressing is amazing. there's also the 6309, a CMOS clone made by hiatchi who secretly added even more features - higher clock speed, more registers, new instructions, a 1-byte cache, and it has a 16-bit ALU so any 16-bit instructions are ~30% faster.

|

|

|

|

Stack Machine posted:The 6809 and 6800 both at least had a 16-bit stack pointer and index register. The 6502 was way down in the weeds on cost vs everything else so of course a ton of home computers used it. All of the popular 8-bit big-endian CPUs call the stack ops push and "pull" so there's going to be uncomfortable cringing involved no matter what. This. And at the time, it was real weird for Nintendo to use the 6502 for the NES too. Their arcade cabs (Donkey Kong, etc) were Z80-based, like pretty much everything else coming out of Japan at the time. The problem was that all of Nintendo's suppliers thought the Famicom was a doomed venture, and none of them would agree to manufacture its CPU, for fear that Nintendo would go bankrupt and leave them with a pile of custom chips that couldn't be easily reused. So Nintendo had to resort to Ricoh, who was a third-string supplier at the time. Ricoh didn't have a Z80 core... but they did have a 6502. And the rest was history.

|

|

|

|

Stack Machine posted:The 6809 and 6800 both at least had a 16-bit stack pointer and index register. The 6502 was way down in the weeds on cost vs everything else so of course a ton of home computers used it. All of the popular 8-bit big-endian CPUs call the stack ops push and "pull" so there's going to be uncomfortable cringing involved no matter what. now the 65816 on the other hand

|

|

|

|

Someone on twitter offered to send me their PS2 dev kit on loan so I might start writing some PS2 software

|

|

|

|

Luigi Thirty posted:now the 65816 on the other hand I can't get past the fact that both the 65816 and the 65C02 have, of all things, a memory lock pin for proper multiprocessor support.

|

|

|

|

Luigi Thirty posted:Someone on twitter offered to send me their PS2 dev kit on loan so I might start writing some PS2 software cubes cubes cubes cubes cubes cubes CUBES CUBES CUBES

|

|

|

|

|

|

|

|

flared base, nice

|

|

|

|

Lutha Mahtin posted:cubes cubes cubes

|

|

|

|

Stack Machine posted:I can't get past the fact that both the 65816 and the 65C02 have, of all things, a memory lock pin for proper multiprocessor support. processor manufacturers were sort of obsessed with multiprocessing in the late 70s/early 80s. the 6809 came in a version called the 6809E that was designed to be the slave CPU that ran from the clock output of a 6809 master, had a tri-stateable bus, and signals for announcing whether or not it was going give up the bus after the current instruction or wanted to use to use the bus during the next cycle. most 8-bit CPUs had bus request/grant pins as well for sharing with another CPU or a DMA controller. nobody ever really built these multi-processor boards though because you had to build your own bus arbitration system out of TTL glue logic, and memory speeds weren't generally up to the task of serving two CPUs without slowing them down so it was rarely worth it.

|

|

|

|

Lutha Mahtin posted:cubes cubes cubes cubes cubes cubes CUBES CUBES CUBES wasn't the ps2 bullshit number 60 million polygons per second? if so, i expect to see.. let's see 60 million / 60fps / (6 sides per cube * 2 polygons).... about 80000 cubes rotating at 60fps.

|

|

|

|

Sweevo posted:processor manufacturers were sort of obsessed with multiprocessing in the late 70s/early 80s. the 6809 came in a version called the 6809E that was designed to be the slave CPU that ran from the clock output of a 6809 master, had a tri-stateable bus, and signals for announcing whether or not it was going give up the bus after the current instruction or wanted to use to use the bus during the next cycle. most 8-bit CPUs had bus request/grant pins as well for sharing with another CPU or a DMA controller. nobody ever really built these multi-processor boards though because you had to build your own bus arbitration system out of TTL glue logic, and memory speeds weren't generally up to the task of serving two CPUs without slowing them down so it was rarely worth it. Namco used dual and triple CPUs a lot in the early 80s there were some microcomputers like the C128 that had a Z80 in addition to their main CPU for CP/M compatibility nothing can top the 80s solution to arcade 3D graphics though which was �throw more DSPs at the problem�: Atari�s final 3D hardware features no less than 5 TI and AT&T DSPs and got its butt mega-kicked by Daytona USA at AMOA

|

|

|

|

afaik tons of stuff had an extra processor for peripheral control and io and similar also, so probably those features were not a bad plan.

|

|

|

|

Luigi Thirty posted:Atari�s final 3D hardware features no less than 5 TI and AT&T DSPs and got its butt mega-kicked by Daytona USA at AMOA

|

|

|

|

Cybernetic Vermin posted:afaik tons of stuff had an extra processor for peripheral control and io and similar also, so probably those features were not a bad plan. most of those had the slave CPU as an entirely separate system that communicated through a few I/O ports rather than a true multiprocessor design with shared memory. a lot of arcade boards had a separate CPU for the sound, but it had it's own ROM and RAM and the main CPU just wrote single-byte commands to an I/O port to tell the sound CPU to "mute all" or "play sample #29" etc

|

|

|

|

Luigi Thirty posted:there were some microcomputers like the C128 that had a Z80 in addition to their main CPU for CP/M compatibility i'm not really familiar with the c128, but didn't it run either the 6502 OR the z80 rather than both at the same time? btw look up Bil Herd on youtube. he has some interesting stories about creating the c128, like the z80 literally only being there because marketing were going around promising the (still unfinished) c128 would be 100% hardware and software compatible with the c64, but he couldn't get the c64 cp/m cartridge to work so he decided to just built it into the machine rather than fix the problem. Sweevo fucked around with this message at 13:47 on Dec 5, 2019 |

|

|

|

Luigi Thirty posted:Namco used dual and triple CPUs a lot in the early 80s well yeha nothing can beat the daytona theme

|

|

|

|

even the ps4 has a weird master/drone setup. it had a whole ARM system to run the dashboard OS and then it drives the ATI CPU/GPU for the heavy lifting, or something like that

|

|

|

|

Sweevo posted:most of those had the slave CPU as an entirely separate system that communicated through a few I/O ports rather than a true multiprocessor design with shared memory. Yeah, iirc for Namco boards it was a main Z80, a sound commands Z80, and a graphics manipulation Z80 nobody can top Sega�s 1980 sprite scaling approach which was �a lookup table for height and VCOs to control the sprite ROM data clock to make sprites wider�

|

|

|

|

Lutha Mahtin posted:even the ps4 has a weird master/drone setup. it had a whole ARM system to run the dashboard OS and then it drives the ATI CPU/GPU for the heavy lifting, or something like that the wii had a similar setup and it's just for handling things like security and background downloads when the system is in standby

|

|

|

|

The_Franz posted:the wii had a similar setup and it's just for handling things like security and background downloads when the system is in standby that's probably what the ps4 uses it for too, it has similar low-power features the arm cpu probably runs the always-on screen recorder

|

|

|

|

Sweevo posted:most of those had the slave CPU as an entirely separate system that communicated through a few I/O ports rather than a true multiprocessor design with shared memory. I have grown to know and hate a board from a friend's Williams Space Shuttle pinball table that just has 2 6800s with a little ROM and RAM for each and a whole poo poo ton of PIAs (antediluvian IO expanders). Its sound setup is exactly this, with a pair of PIAs dedicated to getting sound/speech commands from the main CPU to the sound CPU which then spews samples into a DAC or LPC... things... into a TI speech synth.

|

|

|

|

Luigi Thirty posted:Yeah, iirc for Namco boards it was a main Z80, a sound commands Z80, and a graphics manipulation Z80 wtf that's incredible

|

|

|

|

Endless Mike posted:well yeha nothing can beat the daytona theme well you say that but... PEPSIMAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAN

|

|

|

|

Hunter2 Thompson posted:wtf that's incredible For the time it must've been pretty mind-blowing though.

|

|

|

|

Luigi Thirty posted:nobody can top Sega’s 1980 sprite scaling approach which was “a lookup table for height and VCOs to control the sprite ROM data clock to make sprites wider”  anywhere I can read more about that? anywhere I can read more about that?

|

|

|

|

spankmeister posted:

https://segaretro.org/VCO_Object

|

|

|

|

Stack Machine posted:I have grown to know and hate a board from a friend's Williams Space Shuttle pinball table that just has 2 6800s with a little ROM and RAM for each and a whole poo poo ton of PIAs (antediluvian IO expanders). Its sound setup is exactly this, with a pair of PIAs dedicated to getting sound/speech commands from the main CPU to the sound CPU which then spews samples into a DAC or LPC... things... into a TI speech synth.  Bally used a TI speech synth, talking Williams tables used a Harris CVSD decoder Bally used a TI speech synth, talking Williams tables used a Harris CVSD decoder

|

|

|

|

atari�s first generation 3D hardware for its driving games used - TMS34010@48MHz for rasterization (called GSP) - TMS34010@50MHz for pixel expansion (called PSP) - ADSP2100@8MHz for polygon transforms (called DSP) - 68000@7MHz running the sound program - TMS32010@20MHz for sound output - 68010@to run the game program code and synchronize everything up to 5 boardsets could be linked via serial port for panoramic visuals which they�re smart enough to automatically configure after that they bolted on a DSP32C@40MHz and TMS32015@20MHz (collectively called DSK, Driver Speed Kit) which added a better physics model and more polygon pushing another variant added on another ADSP2100 called DSPCOM because you can�t have enough DSPs the guy who designed the boards left in 1992 and the rest of the team all founded their own car simulation startup which last I checked is still in business making those computers for drivers ed classes

|

|

|

|

|

| # ? Apr 28, 2024 05:23 |

|

Uh, is that how hard drivin worked? Thats a shitload of hardware to move like 100 polygons at 15fps

|

|

|